Last week at the Intel Technology and Manufacturing Day held in Beijing, China, the company gave updates on some of its new technology. Some of the new technology showcased included power and performance updates for Intel’s 10 nm process, high-level plans for Intel’s first 10 nm FPGA, and an announcement the company is shipping the industry’s first commercially available 64-layer 3D NAND for data center applications.

Intel has advanced its manufacturing process according to Moore’s Law, basically they intend to make less expensive products with better performance/capabilities every year. Intel plans on continuing to drive Moore’s Law, while reaping the benefits, as they unveil their new technology.

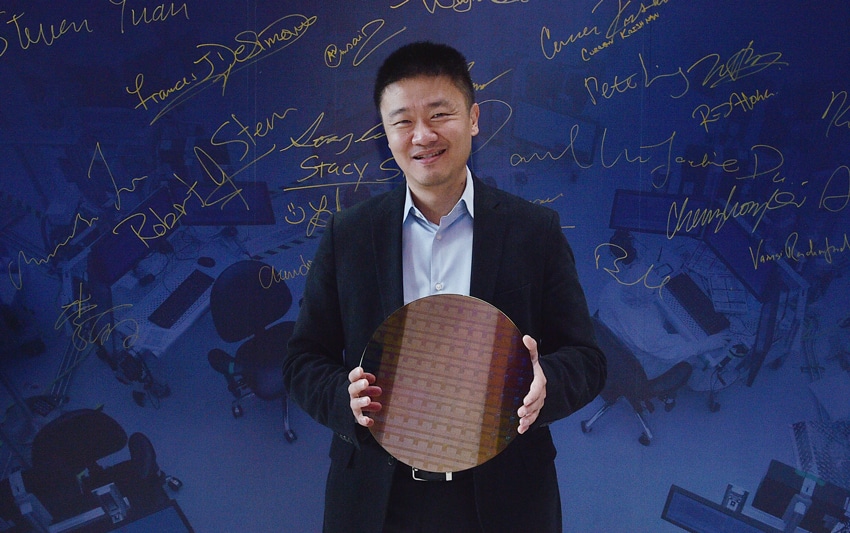

Intel stated that it is a full generation ahead of other 10nm technologies in terms of both transistor density and transistor performance. Touting the world’s tightest transistor and metal pitches, Intel’s 10nm technology is created with hyper scaling, for the highest density in the industry. By hyper scaling, the company is referring to the 2.7x logic transistor density improvement attained on the company’s 14 nm and 10 nm processes. Intel used the event to display its “Cannon Lake” 10nm wafer for the first time.

Intel’s lower-power FinFET technology for mobile applications, 22FFL, was given a power and performance update. The 22FFL hit performance of 2 GHz with ultra-low power of more than 100x lower leakage. As with the “Cannon Lake,” the 22FFL was also on display for the first time.

Intel gave an update on its “Falcon Mesa” technology, a coming generation of FPGAs using the 10nm process technology and foundry platform. The new FPGA was claimed to be able to offer new levels of performance to support the growing bandwidth demands of data center, enterprise and networking environments. Other benefits include:

- 112Gbps serial transceiver links to support the most demanding bandwidth requirements in next-generation data center, enterprise and networking environments.

- Latest peripheral device interconnect including PCI Express Gen4 x16 support with data rates up to 16 GT/s per lane for next-generation data centers.

The company announced that its agreement with ARM and Intel Custom Foundry is proceeding. The agreement centered around accelerating the development and implementation of ARM SoCs on Intel's 10nm process. Intel showed the first results of this agreement in a 10nm wafer containing ARM Cortex-A75 CPU cores implemented with industry standard design flows enabling performance in excess of 3 GHz.

And finally, Intel announcing the it has been shipping the industry’s first 64-layer, triple level cell (TLC), 3D NAND SSD (solid state drive) for data center applications since early August. This NAND is designed to help customers significantly improve storage efficiency. The product is expected to be made more broadly available–it is currently only shipping to select customers–by the end of the year.

Sign up for the StorageReview newsletter