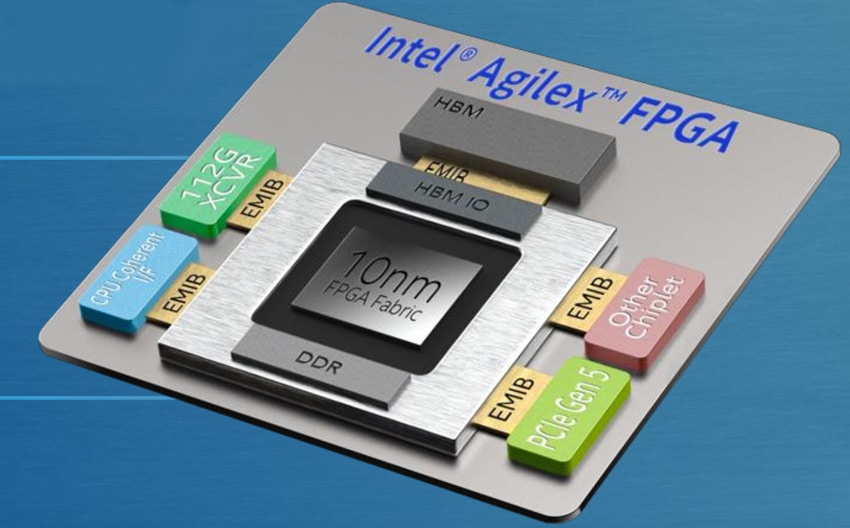

Intel has introduced the new Agilex FPGAs designed to add agility, flexibility and massive bandwidth capabilities. With its high-performance compute build, Intel says these new FPGAs can excel in networking (5G, NFV terabyte OTN), edge and embedded (vision analytics, industry 4.0, smart cities/surveillance, radar and defense), Cloud (application, and network storage acceleration), and Enterprise (financial analytics, database acceleration, genomics) use cases.

It’s quite clear that Intel has designed their new FPGAs for our “data-centric world” with a focus on processing, storing and moving data via features including:

- 2nd generation Intel Hyperflex Architecture

- Up to 40% Higher performance

- Up to 40% Lower Power

- Up to 40 TFLOPS DSP Performance

- DDR5 & HBM with Intel Optane DC Persistent Memory support

- Intel Xeon Processor coherent connectivity & PCIeGen5

- 112G Transceiver data rates (which allows for high bandwidth in applications including 400G networks, edge analytics, data center workloads)

This is also the company’s first cache-coherent (that is, the regularity/consistency of data stored in cache memory) accelerator for Intel Xeon Scalable Processors, which promotes low latency, increased memory space and custom acceleration capabilities. This feature is expected to accelerate diverse workloads such as data analytics, database, and function-as-a-service.

Moreover, Intel indicates that it helps create agile and flexible AI through the following:

- Flexibility for evolving AI workloads and integrating AI with other functions

- Supports low-precision INT7 through INT2 configurations for high performance

- Only FPGA supporting hardened

- BFLOAT16 & FP16

The Intel Agilex FPGA Family includes three different lines: the F-Series, which is designed for a wide range of applications; I-Series, which excels in high-performance processor interface and bandwidth-intensive applications; and the M-Series; which is mainly for compute-intensive applications. Here’s a quick rundown of what each Series offers:

- F -Series

- Up to 58G transceivers

- PCIe Gen4

- DDR4

- Quad-Core ARM Cortex-A53 SoC Option

- I -Series

- Up to 112G transceivers

- PCIe Gen5

- DDR4

- Quad-Core ARM Cortex-A53

- Coherent attach to Intel Xeon Scalable Processor option

- M -Series

- Up to 112G transceivers

- PCIe Gen5

- DDR4, DDR5 and Intel Optane DC Persistent Memory support

- Quad-Core ARM Cortex-A53

- Coherent attach to Intel Xeon Scalable Processor option

- HBM Option

Intel Agilex FPGA also features developer tools to promote higher productivity, claiming 30% increase in compile times, new productivity flows for faster design convergence and new usability features. They are also built to increase efficiency with a 15% improvement in memory utilization while using a single source for a software-friendly heterogeneous programming environment, says Intel. It supports common performance library APIs and Intel software development tools such as Intel VTune Amplifier and Intel Advisor.

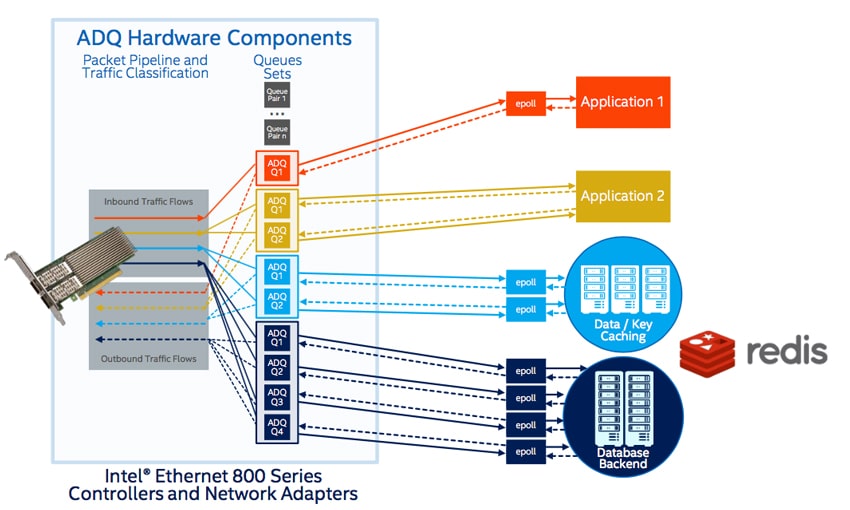

Also announced is the new Intel Ethernet 800 series. This new line is highlighted by queue and steering hardware to assist application device queues (ADQs), technology that improves application performance. They also feature a fully programmable pipeline via dynamic device personalization, which improves packet processing efficiency.

With this new NIC release, Intel puts a huge emphasis on improving application response predictability. They claim that this new focus will reduce variability in application response time (aka. “jitter”). Working to eliminate jitter means that more servers can be added reduce latency (Intel claims more than 45% reduction), application throughput (Intel indicated more than a 30% increase), more support for end-users with existing hardware. The new Intel 800 series does this through its use of ADQ, which was absent from their previous 500 and 700 Series. As noted above, ADQ is an application specific queuing and steering technology. It does this by filtering application traffic to a dedicated set of queues, while application threads of executions are connected to particular queues within the ADQ set.

The new Intel Ethernet 800 Series is also highlighted by Dynamic Device Personalization, which helps improve run-time programmability and optimize performance. It features packet pipeline customization to satisfy a range of different customer deployment needs while lowering latency, higher throughput, and improved CPU utilization. Moreover, it enables 100Gb/s port speeds making it a good choice for those that need to move massive amounts of data in the cloud.

Availability

The Intel Ethernet 800 Series adapter is sampling today, with production scheduled for third quarter of 2019. The new Intel Agilex FPGA family of 10nm FPGAs will start sampling in the second half of 2019.

Sign up for the StorageReview newsletter