L'architettura AMD Zen 5 utilizza un design modulare innovativo, consentendo ad AMD di creare CPU per desktop, server, client e embedded.

Il Tech Day 2024 di AMD ha svelato i dettagli dietro gli ultimi progressi e ha coperto molti argomenti, in particolare con l'ultima CPU Zen 5 e le architetture incentrate sull'intelligenza artificiale XDNA. Questo evento ha sottolineato la visione di AMD di rivoluzionare l'efficienza dell'intelligenza artificiale, le prestazioni energetiche e l'integrazione perfetta tra più applicazioni, riaffermando la sua leadership nel settore dell'informatica ad alte prestazioni.

La collaborazione strategica con Microsoft ha posto le basi per la leadership di AMD nelle esperienze PC AI, offrendo efficienza, prestazioni e integrazione senza precedenti in un'ampia gamma di applicazioni. Le CPU EPYC di quinta generazione, con un massimo di 5 core e 192 thread, promettono miglioramenti significativi in termini di efficienza energetica e accelerazione dell'intelligenza artificiale. Con la previsione avanzata dei rami, i doppi tubi di decodifica e una nuova unità di accelerazione matematica, AMD afferma che Zen 384 offre un miglioramento del 5% nelle prestazioni AES-XTS single-core e un aumento del 35% nelle attività di apprendimento automatico rispetto al suo predecessore. Mentre AMD continua ad ampliare i confini della potenza di elaborazione e dell'efficienza, l'architettura Zen 32 è pronta a rivoluzionare i mercati dei data center e dei server.

L'architettura AMD Zen 5 utilizza un design modulare innovativo, consentendo ad AMD di creare prodotti su misura per applicazioni desktop, server, client e embedded. L'integrazione delle tecnologie di processo a 4 e 3 nm garantisce che i prodotti basati su Zen5 possano offrire prestazioni ottimizzate ed efficienza energetica in diversi casi d'uso.

AMD Zen 5

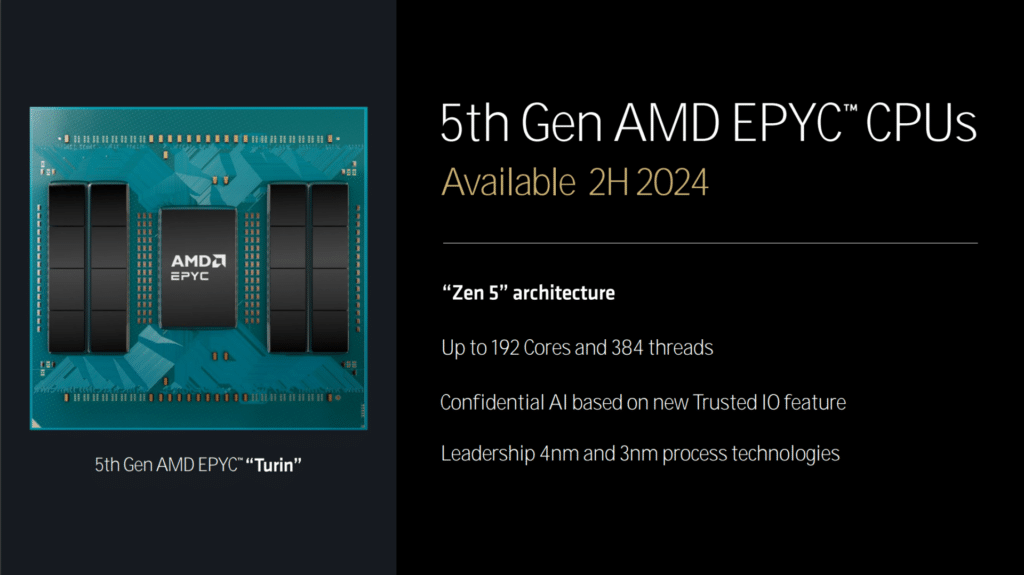

Nella presentazione di AMD al Tech Day 2024, Mark Papermaster ha svelato progressi significativi nell'architettura Zen 5, mettendo in risalto in particolare le CPU EPYC di quinta generazione. La linea EPYC, che sarà lanciata nella seconda metà del 5, promette di offrire prestazioni ed efficienza senza precedenti, spingendo all’estremo i parametri di densità e prestazioni nei mercati dei server e dei data center.

Le CPU EPYC di quinta generazione hanno aumentato significativamente il numero di core e la capacità di threading. Questi miglioramenti includono anche miglioramenti nell’efficienza energetica, resi possibili grazie a una continua collaborazione con TSMC e a uno stack metallico ottimizzato. Quest'ultimo ha migliorato notevolmente le prestazioni termiche ed elettriche. L'architettura sfrutta l'accelerazione IA avanzata introducendo una nuova unità di accelerazione matematica che promette un miglioramento fino al 5% nelle prestazioni AES-XTS single-core e fino al 35% nelle attività di machine learning single-core rispetto a Zen 32.

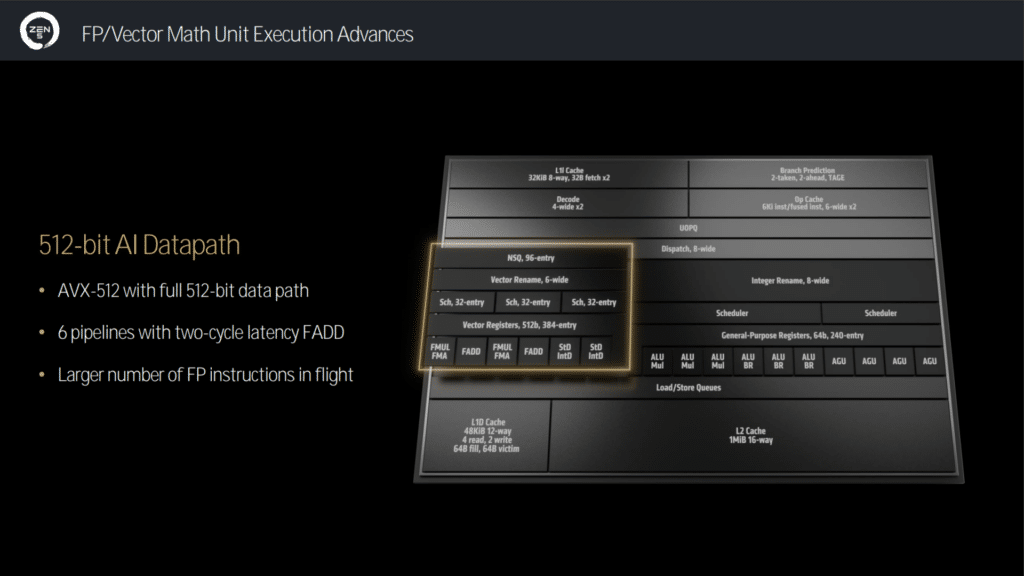

I progressi architettonici di Zen 5 sono completi. Le fasi di recupero e decodifica delle istruzioni sono state migliorate con previsione avanzata dei rami e doppi pipe di decodifica per ridurre la latenza e migliorare la precisione. Le unità di esecuzione intere vedono un aggiornamento sostanziale con funzionalità di invio/ritiro su 8 livelli e uno scheduler ALU più unificato, il tutto all'interno di una finestra di esecuzione più ampia. I miglioramenti in termini di caricamento/archiviazione includono una cache dati L48 a 12 vie da 1 KB con il doppio della larghezza di banda massima sia per la cache L1 che per l'unità a virgola mobile, che è fondamentale per le operazioni con un uso intensivo dei dati.

L'architettura Zen 5 include anche miglioramenti significativi nella larghezza di banda dei dati. I miglioramenti di caricamento/archiviazione, con una cache dati L48 a 12 vie da 1 KB, offrono il doppio della larghezza di banda massima per la cache L1 e l'unità a virgola mobile, essenziale per le operazioni ad uso intensivo di dati. La capacità dell'architettura di gestire un numero maggiore di istruzioni in virgola mobile in volo, con AVX-512 e un percorso dati completo a 512 bit, garantisce sostanziali miglioramenti delle prestazioni nei carichi di lavoro AI e vettoriali.

Anche l'esecuzione di unità matematiche in virgola mobile e vettoriale ha visto miglioramenti significativi. L'AVX-512, con un percorso dati completo a 512 bit e sei pipeline (che offrono una latenza di due cicli per operazioni di aggiunta in virgola mobile), migliora significativamente la capacità di gestire istruzioni simultanee in virgola mobile. Ciò avvantaggia in particolare i carichi di lavoro vettoriali e di intelligenza artificiale, consentendo miglioramenti significativi delle prestazioni nell’apprendimento automatico e nelle attività ad alta intensità di dati. Ciò contrasta con Zen 4, dove AMD ha "doppiato" il percorso a 256 bit per ottenere prestazioni a 512 bit.

Zen 5 offre un aumento medio dell'IPC del 16% per i processori desktop e mobili rispetto al suo predecessore, Zen 4. Ciò è ottenuto attraverso perfezionamenti dell'architettura, tra cui unità di invio ed esecuzione più ampie, maggiore larghezza di banda dei dati e algoritmi di precaricamento migliorati. I guadagni IPC si traducono in miglioramenti delle prestazioni nel mondo reale in varie applicazioni, dai giochi alla creazione di contenuti e all’apprendimento automatico.

Sul fronte GPU, AMD continua a ottimizzare la sua architettura RDNA 3 per l'efficienza in termini di prestazioni energetiche. AMD dichiara prestazioni per watt fino al 32% più elevate rispetto alle precedenti CPU Ryzen. Ciò è possibile grazie a una migliore gestione della memoria, operazioni comuni sulle texture di gioco a velocità doppia e funzionalità avanzate di gestione dell'energia.

L'architettura Zen 5 di AMD rappresenta un'evoluzione impressionante dell'architettura Zen, in particolare per la linea EPYC, che promette di aumentare gli standard di prestazioni su tutta la linea, dai mercati desktop e mobili ai server e ai data center. Con miglioramenti significativi nel numero di core, threading, efficienza energetica e accelerazione dell'intelligenza artificiale in alcuni chip, le CPU EPYC di quinta generazione sono posizionate per soddisfare le crescenti esigenze dei moderni carichi di lavoro incentrati sui dati.

xDNA

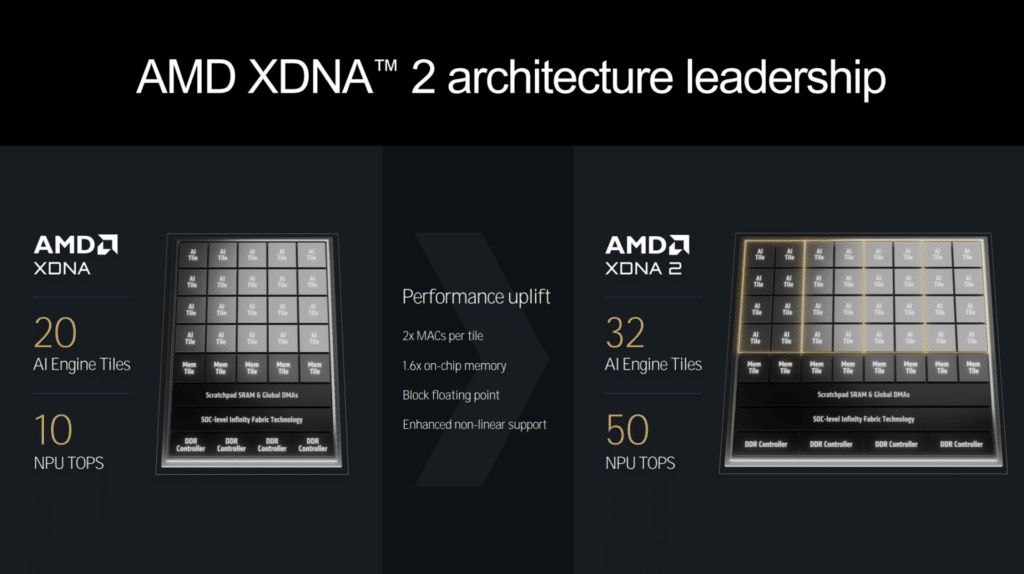

Vamsi Boppana, vicepresidente senior dell'Artificial Intelligence Group, ha delineato il potenziale di trasformazione della nuova architettura incentrata sull'intelligenza artificiale di AMD. La crescita esponenziale e la specializzazione dei carichi di lavoro AI richiedono architetture di calcolo innovative e la risposta di AMD è l'introduzione dell'architettura XDNA 2.

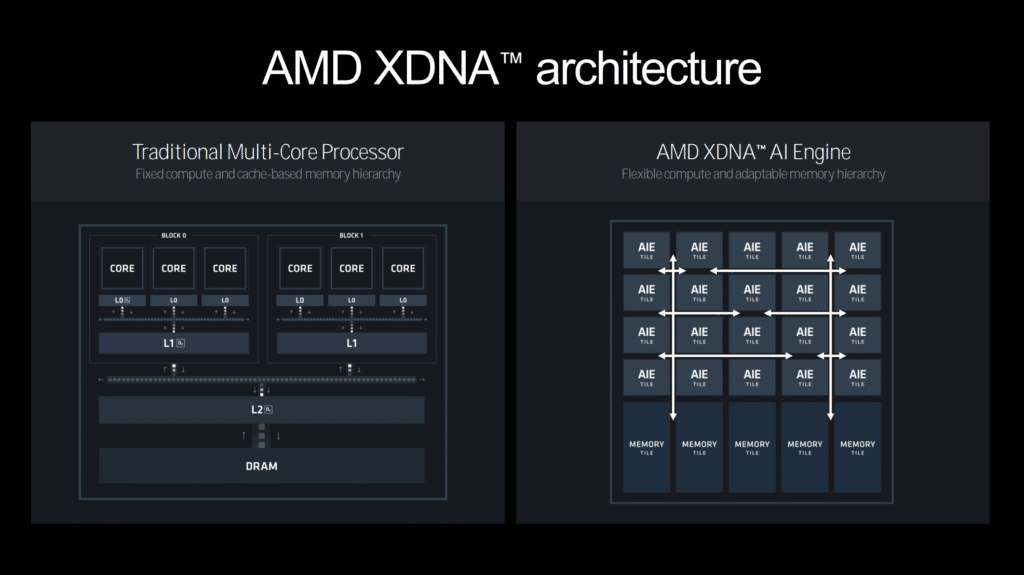

Al centro di questa innovazione c’è l’architettura AMD XDNA, nota per la sua eredità in diverse applicazioni AI e DSP, che spaziano dalla comunicazione, all’implementazione del 5G, all’elaborazione del segnale radar di difesa, all’elaborazione AI trasmessa in tempo reale per punti di vista 3D e all’elaborazione di immagini sanitarie. L'architettura si sposta dalle tradizionali gerarchie di memoria basate su calcolo fisso e cache a un modello più flessibile e adattabile. Questa riconfigurabilità spaziale e l'architettura del flusso di dati piastrellato consentono un multitasking efficiente e prestazioni in tempo reale garantite.

La presentazione ha evidenziato il processore x86 di AMD con NPU integrata, progettato per offrire efficienza e prestazioni elevate per i carichi di lavoro AI. I processori AMD Ryzen AI di terza generazione vantano progressi significativi nelle capacità NPU, raggiungendo fino a 3 TOPS (trilioni di operazioni al secondo) e incorporando fino a 50 core CPU e 12 unità di calcolo GPU. Questi processori sono destinati a supportare oltre 16 esperienze basate sull’intelligenza artificiale su piattaforme come Adobe, Black Magic e Topaz Labs, rendendoli centrali per le esperienze PC AI di prossima generazione.

Il motore AI all'interno dell'architettura XDNA 2 include il supporto migliorato per diversi tipi di dati, come INT8 e Block FP16, che garantiscono prestazioni elevate e precisione in una gamma di applicazioni AI. L'architettura AI adattiva consente un'integrazione scalabile nel portafoglio di prodotti AMD, offrendo multitasking efficiente e prestazioni in tempo reale garantite attraverso la riconfigurabilità spaziale e un'architettura del flusso di dati piastrellata.

Il blocco FP16, in particolare, consente una sostituzione immediata dei modelli FP32 con una perdita di precisione minima o nulla, rendendolo altamente efficiente per attività come la generazione di immagini, modelli linguistici ed elaborazione audio e video in tempo reale.

Una caratteristica straordinaria è la possibilità di configurare la struttura XDNA in fase di runtime. Ciò consente flessibilità con i percorsi dati e la segmentazione della NPU per eseguire contemporaneamente più modelli di diverse dimensioni. Fornisce inoltre la flessibilità necessaria per offrire esperienze basate sull'intelligenza artificiale come Copilot+ per una maggiore produttività e una collaborazione coinvolgente. L'integrazione dello stack software AI unificato tra i componenti CPU, GPU e NPU di AMD consente un ampio supporto di modelli e prestazioni ottimizzate, rendendo più semplice per gli sviluppatori distribuire migliaia di modelli AI in modo rapido ed efficace.

L'architettura AMD XDNA 2 dimostra un salto significativo nella tecnologia AI. Con un massimo di otto flussi spaziali simultanei, raddoppia l'efficienza energetica delle generazioni precedenti. Ciò rende la soluzione di AMD potente ed estremamente efficiente, aprendo la strada a una nuova era di applicazioni AI nei PC e oltre.

I processori AMD Ryzen AI di terza generazione offrono inoltre una maggiore sicurezza introducendo nuove funzionalità Trusted IO. Questo miglioramento della sicurezza è fondamentale per proteggere i dati sensibili e garantire prestazioni affidabili nelle applicazioni basate sull’intelligenza artificiale, rafforzando l’impegno di AMD verso soluzioni AI sicure ed efficienti.

Specifiche AMD Zen 5 e XDNA 2

| Architettura Zen 5 | |

| caratteristica | Dettagli |

| Tecnologia di processo | 4 nm e 3 nm |

| Core Count | Fino a 192 core |

| numero di thread | Fino a 384 thread |

| Cache | Cache dati L48 a 12 vie da 1 KB |

| Larghezza di banda | Raddoppia la larghezza di banda massima per la cache L1 e l'unità a virgola mobile |

| Esecuzione di numeri interi | Spedizione/ritiro di larghezza 8, 6 ALU, 3 moltiplicazioni |

| Esecuzione in virgola mobile | AVX-512 con percorso dati completo a 512 bit, 6 pipeline |

| Accelerazione AI | Nuova unità di accelerazione matematica |

| Incremento IPC | Aumento medio dell'IPC del 16% rispetto a Zen 4 |

| Guadagni in termini di prestazioni | Miglioramento del 35% in AES-XTS single-core, aumento del 32% nelle attività di machine learning |

| Efficienza energetica | Ottimizzato per prestazioni/watt con stack metallico migliorato |

| Applicazioni del prodotto | Desktop, dispositivi mobili, server e data center |

| Architettura XDNA 2 | |

| Riquadri del motore AI | Fino a 32 |

| Prestazioni dell'IA | Fino a 50 TOP |

| Core Count | Fino a 12 core della CPU |

| Unità di calcolo GPU | Fino a 16 |

| Tipi di dati supportati | INT8, blocco FP16 |

| EFFICIENZA | Efficienza energetica 2 volte superiore rispetto alla generazione precedente |

| Flussi concorrenti | Fino a 8 |

| Sicurezza | Nuove funzionalità IO attendibili |

| Pila di software | Stack software AI unificato su CPU, GPU e NPU |

| Prestazioni in tempo reale | Prestazioni in tempo reale garantite con l'architettura spaziale |

| Applicazioni | Giochi, intrattenimento, assistenza personale tramite intelligenza artificiale, creazione di contenuti, produttività aziendale |

Overclock del desktop Zen 5 con Curve Shaper

Il Curve Optimizer di AMD, una caratteristica distintiva della serie Ryzen 7000, consente agli utenti di abilitare il ridimensionamento dinamico della tensione o l'undervolting compatibile con PMFW/PBO. Questo potente strumento sposta dinamicamente la curva di tensione attraverso passaggi regolabili di "Curve Optimizer", fornendo tensione variabile attraverso lo spettro di frequenza, con più tensione allocata alle frequenze più alte. Gli utenti possono applicare questa ottimizzazione per core, per CCD o per CPU, consentendo un controllo granulare sulle prestazioni e sull'efficienza della propria CPU.

Basandosi sulle fondamenta di Curve Optimizer, AMD introduce Curve Shaper, un sofisticato miglioramento che consente agli utenti di rimodellare le curve di tensione sottostanti per massimizzare il potenziale di sottotensione. Curve Shaper utilizza gli stessi passaggi del suo predecessore. Tuttavia, garantisce agli utenti la flessibilità di aggiungere o rimuovere selettivamente passaggi da 15 distinte bande di frequenza-temperatura (tre bande di temperatura e cinque bande di frequenza). Questa funzionalità di regolazione fine consente agli utenti di ridurre ulteriormente la tensione nelle bande stabili aggiungendo tensione nelle aree in cui si osservano instabilità. La curva rimodellata viene applicata uniformemente su tutti i core, che può essere ulteriormente regolata utilizzando l'ottimizzatore della curva.

Pensieri di chiusura

L'AMD Tech Day 2024 è stato un grande evento in cui abbiamo avuto l'apprezzata opportunità di approfondire le conoscenze degli ingegneri dietro i prodotti. Gli ultimi progressi di AMD con l'architettura XDNA 2 e le CPU Zen 5 evidenziano il suo impegno nel guidare la rivoluzione dell'intelligenza artificiale e dell'informatica ad alte prestazioni. Con miglioramenti rivoluzionari nel numero di core, threading, efficienza energetica e accelerazione dell'intelligenza artificiale, AMD è destinata a ridefinire gli standard di settore e a soddisfare le crescenti richieste dei moderni carichi di lavoro incentrati sui dati, garantendo prestazioni estese su applicazioni desktop, mobili, server e data center.

Interagisci con StorageReview

Newsletter | YouTube | Podcast iTunes/Spotify | Instagram | Twitter | TikTok | RSS feed