本日、インテルは多くの発表の中で、新しいインテル Stratix 10 NX FPGA を発表しました。新しい FPGA は AI に最適化されており、AI アクセラレーションに必要なより高い帯域幅とより低いレイテンシを備えています。 Intel は、新しい FPGA は、自然言語処理や不正行為検出などの計算要求の高いアプリケーション向けに、カスタマイズ可能、再構成可能、スケーラブルな AI アクセラレーションを実現すると述べています。

本日、インテルは多くの発表の中で、新しいインテル Stratix 10 NX FPGA を発表しました。新しい FPGA は AI に最適化されており、AI アクセラレーションに必要なより高い帯域幅とより低いレイテンシを備えています。 Intel は、新しい FPGA は、自然言語処理や不正行為検出などの計算要求の高いアプリケーション向けに、カスタマイズ可能、再構成可能、スケーラブルな AI アクセラレーションを実現すると述べています。

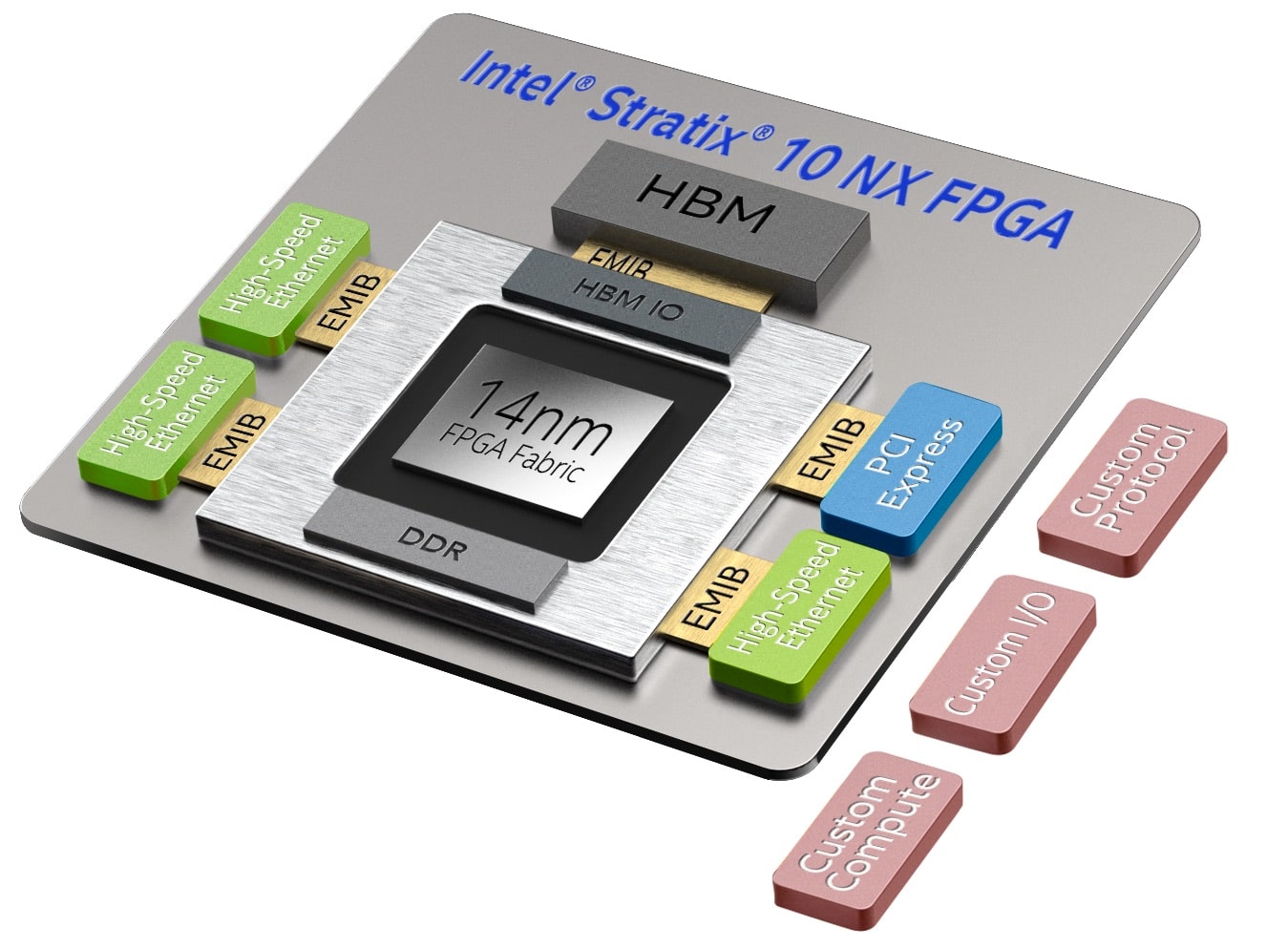

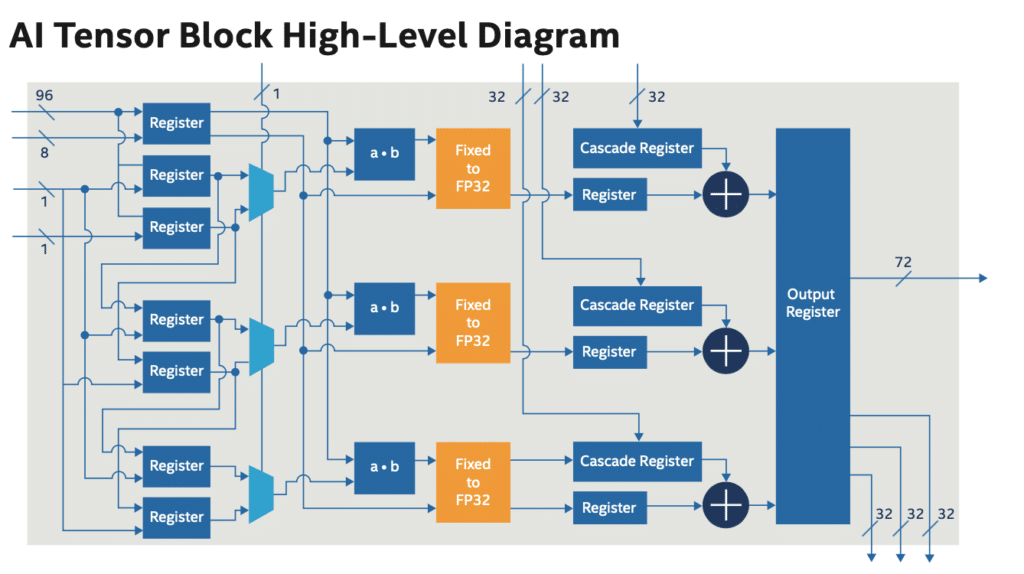

今日インテルが発表したものと同様、新しい FPGA はすべて AI に関するものです。新しい FPGA により、顧客は AI ワークロードを調整できるようになります。必要なパフォーマンスとレイテンシを実現するために、FPGA には統合された高帯域幅メモリ (HBM)、高性能ネットワーキング機能が搭載されています。ただし、Intel の大きなイノベーションは、AI Tensor Blocks と呼ばれる新しい AI に最適化された算術ブロックです。同社によれば、これらのブロックには、AI アプリケーションで通常使用される低精度の乗算器の高密度アレイが含まれています。新しいブロックのアーキテクチャは、小さな行列サイズと大きな行列サイズの両方で動作するように設計された機能を備えた、一般的な行列間の乗算またはベクトルと行列の乗算向けに調整されています。

新しい FPGA は、より高い計算密度、メモリ帯域幅、複数のノードにわたるスケーラビリティ、および再構成可能なカスタム関数を必要とする、低レイテンシで大規模な AI モデルへの傾向に対処するのに独自に適しています。

インテル Stratix 10 NX FPGA の主要な属性:

- AI Tensor ブロック: AI 演算用に調整された AI Tensor ブロックは、高スループット AI 推論アプリケーションに必要な高い計算密度を実現するために、標準のインテル Stratix 15 FPGA DSP ブロック 8 よりも最大 10 倍の INT1 スループットを提供すると推定されています。

- パッケージ内 3D スタック HBM2 高帯域幅 DRAM: 統合メモリ スタックにより、大規模で永続的な AI モデルをオンチップに保存できるため、大きなメモリ帯域幅でレイテンシが短縮され、大規模モデルでのメモリに制約されたパフォーマンスの問題を回避できます。

- トランシーバー・データレート: 最大 57.8 G PAM4 トランシーバーを備えたインテル Stratix 10 NX FPGA は、マルチノード AI 推論ソリューションを実装するための拡張性と柔軟性を提供し、マルチノード設計の制限要因である帯域幅接続を削減または排除します。インテル Stratix 10 NX FPGA には、PCI Express Gen3 x16 および 10/25/100G イーサネット・メディア・アクセス制御 (MAC)/物理コーディング・サブレイヤー (PCS)/前方誤り訂正 (FEC) などのハード知的財産 (IP) も組み込まれています。これらのトランシーバーは、市場の要件に適応するスケーラブルで柔軟な接続ソリューションを提供します。

利用状況

インテル Stratix 10 NX FPGAは、2020 年後半に発売される予定です。

StorageReview と連携する

ニュースレター | YouTube |ポッドキャスト iTunes/Spotifyは | Instagram | Twitter | Facebook | RSSフィード