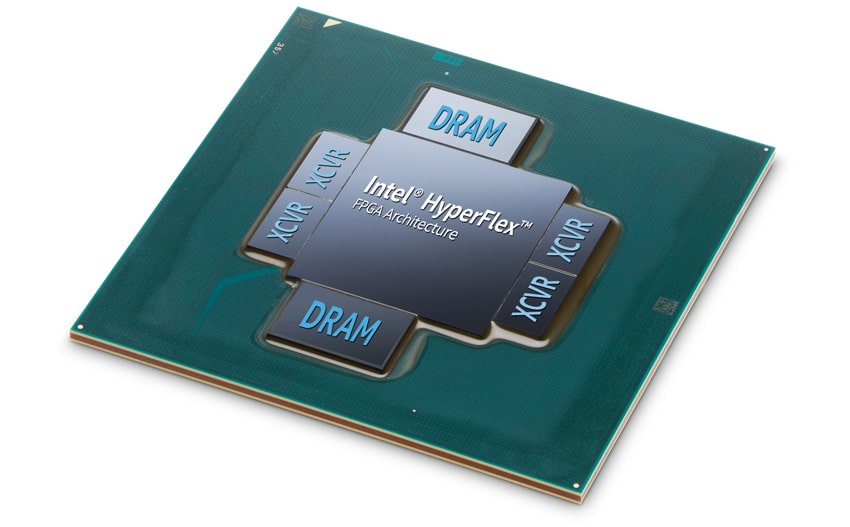

Intel unveiled its latest field programmable gate array (FPGA), the Intel Stratix 10 MX FPGA. What is most notable about this FPGA is that it is the indusry’s first to be integrated with High Bandwidth Memory DRAM (HBM2). Intel states that its new FPGAs will offer up to 10 times the memory bandwidth when compared with standalone DDR memory solutions.

Intel unveiled its latest field programmable gate array (FPGA), the Intel Stratix 10 MX FPGA. What is most notable about this FPGA is that it is the indusry’s first to be integrated with High Bandwidth Memory DRAM (HBM2). Intel states that its new FPGAs will offer up to 10 times the memory bandwidth when compared with standalone DDR memory solutions.

Intel unveiled its latest field programmable gate array (FPGA), the Intel Stratix 10 MX FPGA. What is most notable about this FPGA is that it is the indusry’s first to be integrated with High Bandwidth Memory DRAM (HBM2). Intel states that its new FPGAs will offer up to 10 times the memory bandwidth when compared with standalone DDR memory solutions.

HPC is a field that has really been taking off over the last few years as more and more use cases seem to fit. A need for HPC environments is the ability to compress and decompress data before or after mass data movements. This is an issue that the new Intel Stratix 10 MX FPGA is uniquely designed to address. With its new HBM2-base, the new FPGA can compress and accelerate larger data movements compared to FPGAs without the integrated memory. The company states that the Stratix 10 MX FPGA can simultaneously read/write data and encrypt/decrypt data in real-time without burdening the host CPU resources making it ideal for Apache Kafka and Apache Spark.

In order to get the HBM2 to fit on the FPGA, Intel stacked the DRAM layers vertically using TSV technology and connected it to the FPGA with high density micro bumps. The Stratix 10 MX FPGA family leverages Intel’s Embedded Multi-Die Interconnect Bridge (EMIB). According to Intel, the EMIB works to efficiently integrate HBM2 with a high-performance monolithic FPGA fabric, solving the memory bandwidth bottleneck in a power-efficient manner. This can result in a maximum memory bandwidth of 512 gigabytes per second.

Availability

Intel is currently shipping Stratix 10 FPGA family variants.

Sign up for the StorageReview newsletter