Synopsys unveils industry-first Ultra Ethernet IP and UALink IP solutions to support hyperscale data center infrastructures.

Synopsys has announced the industry’s first Ultra Ethernet IP and UALink IP solutions, engineered to meet the increasing demand for high-bandwidth, low-latency interconnects essential for modern AI and high-performance computing (HPC) architectures. Designed to support hyperscale data center infrastructures, these solutions provide a scalable and standards-based approach for connecting AI accelerators and achieving the performance required to process trillions of parameters in large language models (LLMs).

3D rendering of cyberpunk AI. Circuit board.

Neeraj Paliwal, Senior Vice President of IP Product Management at Synopsys, said:

“With over 25 years of leadership in delivering best-in-class IP solutions, Synopsys continues to accelerate the development of next-generation chips. These groundbreaking Ultra Ethernet and UALink IP solutions allow companies to develop scalable, interoperable HPC and AI infrastructures tailored to the demands of the future.”

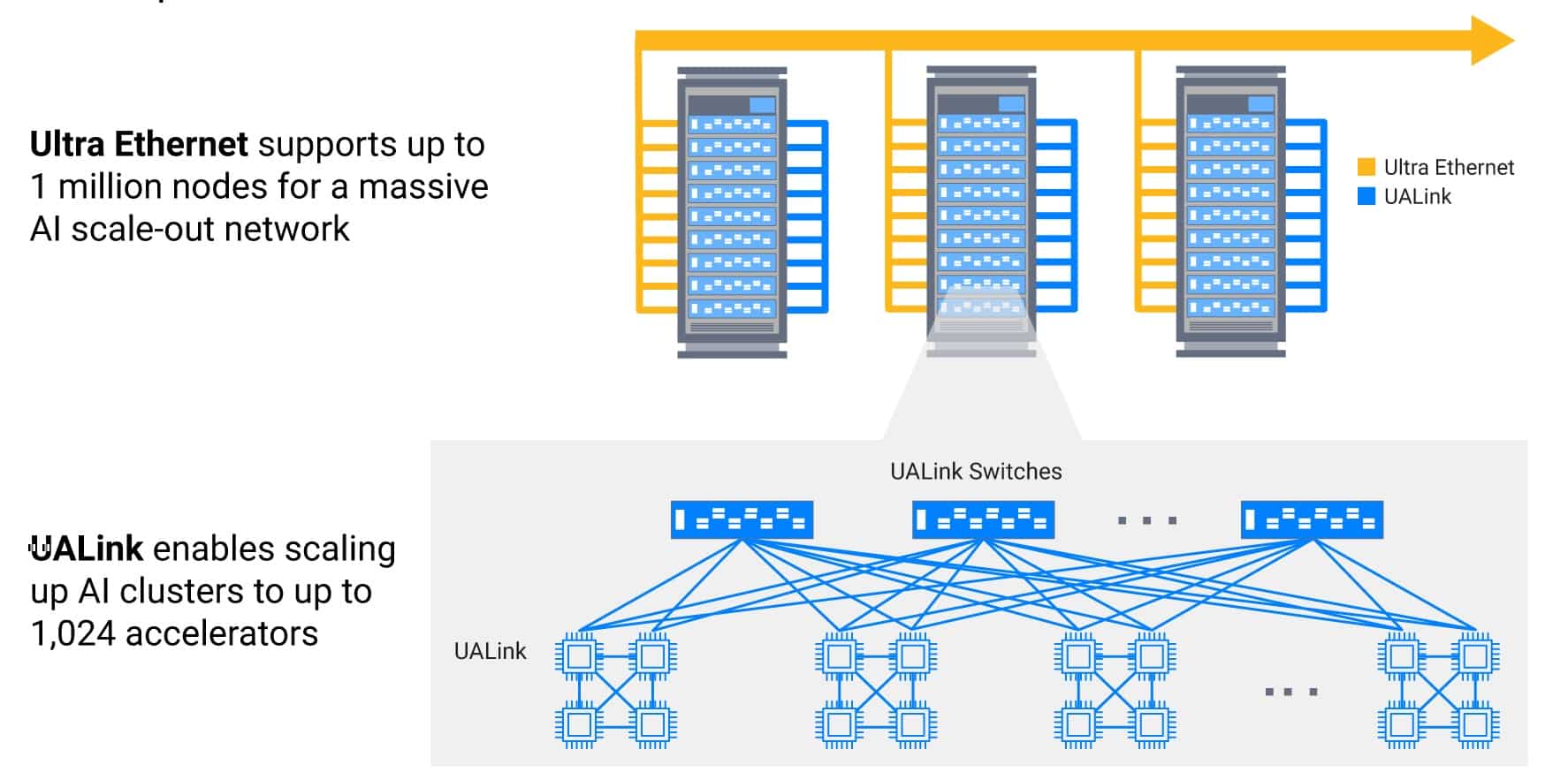

Synopsys Ultra Ethernet IP Solution: Scaling to One Million Endpoints

The Synopsys Ultra Ethernet IP solution redefines network scalability for hyperscale data centers and AI infrastructures by offering advanced interconnect capabilities to support up to one million endpoints in a single network. Its key features include:

- Comprehensive Backend Networking Solution: The IP solution includes Ethernet PHY, MAC, and PCS controllers, along with verification IP. This fully integrated package provides designers with a low-risk pathway to develop large-scale systems with exceptional scalability.

- 224G Ethernet PHY IP for Ultra-Broad Interoperability: The silicon-proven 224G Ethernet PHY IP has demonstrated interoperability at major industry events such as ECOC, OFC, and DesignCon. This ensures compatibility with evolving AI and HPC standards.

- Error Correction for Real-Time AI Workloads: The Ultra Ethernet MAC and PCS controller IP delivers up to 1.6 Tbps of bandwidth with ultra-low latency, a critical requirement for the real-time processing of AI workloads.

- Seamless System Integration: The solution’s MAC and PCS IP integrate seamlessly with higher layers of the Ultra Ethernet stack, enabling implementation across AI accelerators, smart NICs, and switches.

- Accelerated Verification and Standards Compliance: The Synopsys Ultra Ethernet Verification IP ensures adherence to rapidly evolving standards, providing faster validation cycles for large-scale HPC and AI systems.

Synopsys UALink IP Solution: Scaling AI Compute Fabrics

The Synopsys UALink IP solution is designed to scale up AI computing fabrics, providing efficient interconnect capabilities for systems with up to 1,024 AI accelerators. Key features include:

- Optimized Fabric Scaling: The solution includes PHY, controller, and verification IP to facilitate the development of large-scale AI systems, reducing time-to-market for designers.

- High-Speed Data Transfers for AI Workloads: The UALink PHY IP supports 200 Gbps per lane, enabling efficient data movement for the intensive demands of modern AI processing.

- Memory Sharing for Latency Optimization: The UALink Controller IP mitigates bottlenecks by enabling synchronization and memory sharing across accelerators, optimizing performance for distributed AI hardware infrastructures.

- Reliable Protocol Checks for Robust Verification: Synopsys integrates its UALink Verification IP with hardware-assisted verification tools to ensure rapid and reliable testing, further reducing development time for AI solutions.

Advantages for AI and HPC Infrastructure

These groundbreaking solutions are tailored for the challenges of hyperscale AI environments, offering multiple benefits:

- Scalability: The Ultra Ethernet IP solution scales out to one million endpoints, while the UALink IP solution scales up to 1,024 accelerators, accommodating both scale-out and scale-up AI architectures.

- Performance: These IP solutions address the growing computational demands of large language models and AI inference workloads by combining high-speed data transfer capabilities with ultra-low latency.

- Reliability: Advanced error correction and built-in protocol checks ensure robust system performance and compliance with evolving AI and HPC standards.

- Interoperability: The silicon-proven 224G Ethernet PHY IP and other components deliver compatibility across multiple platforms, enabling seamless integration into existing and emerging systems.

Availability

- The Synopsys Ultra Ethernet IP solution, including MAC, PCS, PHY, and verification IP, will be available in the first half of 2025.

- The Synopsys UALink IP solution, encompassing the controller, PHY, and verification IP, is scheduled for release in the second half of 2025.

A New Era for AI and HPC Interconnects

The Synopsys Ultra Ethernet and UALink IP solutions significantly leap forward in enabling high-performance AI and HPC infrastructures. By providing scalable, interoperable, low-risk IP solutions, Synopsys empowers designers to build next-generation systems that meet the demands of increasingly complex AI workloads and hyperscale environments.

Engage with StorageReview

Newsletter | YouTube | Podcast iTunes/Spotify | Instagram | Twitter | TikTok | RSS Feed