IBM revela arquitetura Telum II e Spyre Accelerator na Hot Chips 2024.

A IBM revelou os detalhes da arquitetura para seu próximo IBM Telum II Processor e IBM Spyre Accelerator na conferência Hot Chips 2024. Essas novas tecnologias são projetadas para dimensionar significativamente a capacidade de processamento em sistemas mainframe IBM Z de próxima geração, permitindo a aceleração de modelos de IA tradicionais e modelos de IA de grande linguagem por meio de um novo método de conjunto de IA. À medida que muitos projetos de IA generativa que alavancam Large Language Models (LLMs) transitam da prova de conceito para a produção, a demanda das empresas por soluções escaláveis, seguras e com eficiência energética se tornou uma prioridade máxima.

De acordo com uma pesquisa do Morgan Stanley, espera-se que as demandas de energia para IA generativa aumentem em 75% ao ano nos próximos anos, com projeções indicando que o consumo de energia da IA pode se igualar ao da Espanha até 2026. Isso levou os clientes da IBM a priorizar decisões arquitetônicas que suportem modelos de base de tamanho apropriado e abordagens híbridas por design para cargas de trabalho de IA.

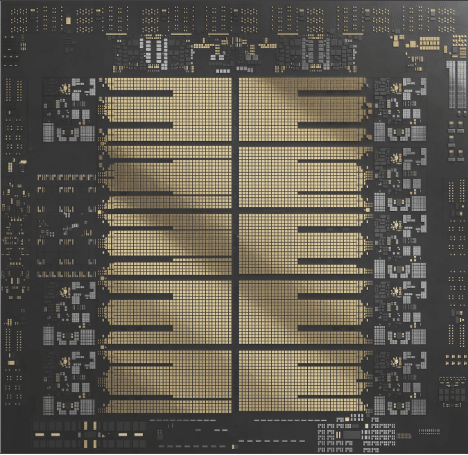

O processador IBM Telum II foi projetado para alimentar a próxima geração de sistemas IBM Z. Ele apresenta frequência aumentada, capacidade de memória expandida, um crescimento de 40% no cache e um núcleo acelerador de IA integrado. O novo processador introduz uma Unidade de Processamento de Dados (DPU) conectada de forma coerente, projetada para acelerar protocolos de E/S complexos para rede e armazenamento no mainframe. A DPU simplifica as operações do sistema e aprimora o desempenho dos componentes principais, tornando o processador Telum II bem adequado para soluções de computação empresarial que dão suporte a LLMs e às complexas necessidades de transações do setor.

Complementando o Telum II Processor está o IBM Spyre Accelerator, fornecendo recursos adicionais de computação de IA. Juntos, os chips Telum II e Spyre formam uma arquitetura escalável que suporta métodos de conjunto de modelagem de IA — combinando vários modelos de IA de aprendizado de máquina ou aprendizado profundo com LLMs de codificador. Essa abordagem de conjunto aproveita os pontos fortes de cada arquitetura de modelo para fornecer resultados mais precisos e robustos em comparação com modelos individuais. O IBM Spyre Accelerator, apresentado como uma prévia no Hot Chips 2024, estará disponível como uma opção complementar. Ele é conectado por meio de um adaptador PCIe de 75 watts e é escalável para atender às necessidades do cliente.

Tina Tarquinio, VP de Gerenciamento de Produtos para IBM Z e LinuxONE, enfatizou o comprometimento da IBM em se manter à frente das tendências tecnológicas, particularmente as crescentes demandas de IA. Ela afirmou que o Telum II Processor e o Spyre Accelerator são projetados para fornecer soluções de computação empresarial de alto desempenho, seguras e com baixo consumo de energia. Essas inovações, que estão em desenvolvimento há anos, serão introduzidas na plataforma IBM Z de próxima geração da IBM, permitindo que os clientes aproveitem LLMs e IA generativa em escala.

O processador Telum II e o IBM Spyre Accelerator serão fabricados pelo parceiro de longa data da IBM, Samsung Foundry, usando seu nó de processo de 5 nm de alto desempenho e eficiência energética. Juntas, essas tecnologias darão suporte a uma variedade de casos de uso avançados baseados em IA, projetados para desbloquear valor comercial e criar novas vantagens competitivas. Por exemplo, a detecção aprimorada de fraudes em reivindicações de seguro residencial pode ser obtida por meio de modelos de IA de conjunto que combinam LLMs com redes neurais tradicionais. Além disso, a detecção avançada de atividades financeiras suspeitas pode ajudar a dar suporte à conformidade com os requisitos regulatórios e mitigar o risco de crimes econômicos. Ao mesmo tempo, os assistentes de IA podem acelerar os ciclos de vida dos aplicativos, transferir conhecimento e fornecer explicações e transformações de código.

O processador Telum II está configurado para apresentar oito núcleos de alto desempenho rodando a 5.5 GHz, com 36 MB de cache L2 por núcleo e um aumento de 40% na capacidade de cache no chip, totalizando 360 MB. O cache virtual de nível 4 oferecerá 2.88 GB por gaveta do processador, um aumento de 40% em relação à geração anterior. O acelerador de IA integrado permite inferência de IA em transações de baixa latência e alto rendimento, proporcionando um aumento de quatro vezes na capacidade de computação por chip em comparação com a última geração. Além disso, a nova Unidade de Aceleração de E/S DPU, integrada ao chip Telum II, foi projetada para melhorar o manuseio de dados com um aumento de 50% na densidade de E/S, aprimorando a eficiência geral e a escalabilidade do IBM Z para cargas de trabalho de IA em larga escala e aplicativos com uso intensivo de dados.

O IBM Spyre Accelerator é um acelerador de nível empresarial desenvolvido especificamente para lidar com modelos de IA complexos e casos de uso de IA generativa. Ele apresenta até 1 TB de memória, distribuído em oito cartões em uma gaveta de E/S regular, suportando cargas de trabalho de modelo de IA no mainframe enquanto consome não mais do que 75 W por cartão. Cada chip tem 32 núcleos de computação que suportam os tipos de dados int4, int8, fp8 e fp16, permitindo aplicativos de IA de baixa latência e alto rendimento.

O processador Telum II alimentará as plataformas IBM Z e IBM LinuxONE de próxima geração da IBM e estará disponível em 2025. O IBM Spyre Accelerator, atualmente em fase de pré-visualização tecnológica, deverá estar disponível em 2025.

Envolva-se com a StorageReview

Newsletter | YouTube | Podcast iTunes/Spotify | Instagram | Twitter | TikTok | RSS feed