Die AMD Zen 5-Architektur verwendet ein innovatives modulares Design, das es AMD ermöglicht, CPUs für Desktops, Server, Clients und eingebettete Systeme zu erstellen.

AMDs Tech Day 2024 enthüllte die Details hinter den neuesten Fortschritten und deckte viele Bereiche ab, insbesondere mit ihrer neuesten Zen 5-CPU und den XDNA AI-zentrierten Architekturen. Diese Veranstaltung betonte AMDs Vision, die KI-Effizienz, die Leistungsleistung und die nahtlose Integration mehrerer Anwendungen zu revolutionieren und bekräftigte damit seine Führungsrolle im Bereich des Hochleistungsrechnens.

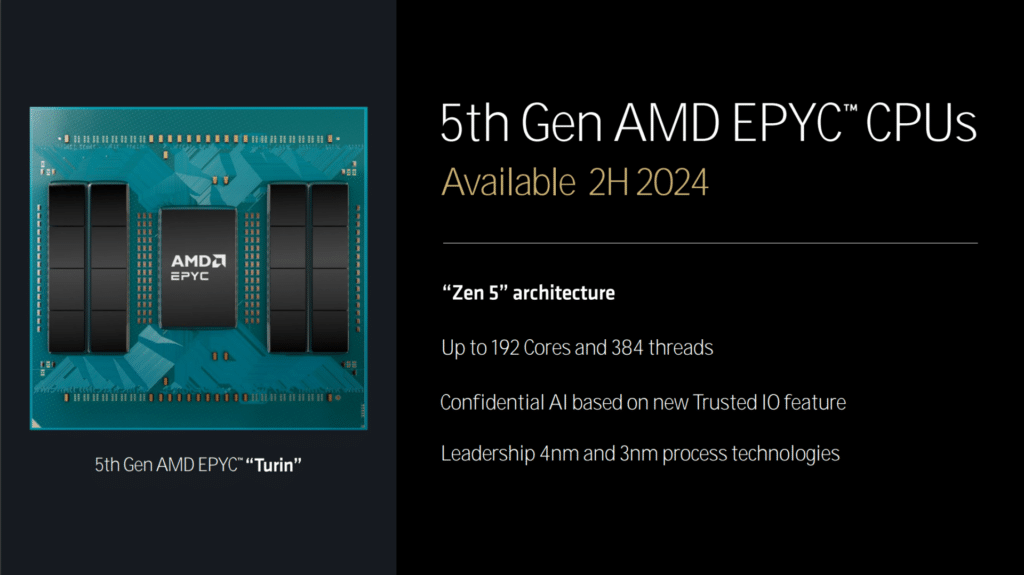

Die strategische Zusammenarbeit mit Microsoft hat AMDs Führungsrolle bei KI-PC-Erlebnissen gefestigt und beispiellose Effizienz, Leistung und Integration für eine breite Palette von Anwendungen geboten. Die EPYC-CPUs der 5. Generation mit bis zu 192 Kernen und 384 Threads versprechen deutliche Verbesserungen bei Energieeffizienz und KI-Beschleunigung. Mit erweiterter Verzweigungsvorhersage, dualen Dekodierungspipes und einer neuen Math Acceleration Unit bietet Zen 5 laut AMD eine 35 %ige Verbesserung der Single-Core-AES-XTS-Leistung und eine 32 %ige Steigerung bei maschinellen Lernaufgaben im Vergleich zum Vorgänger. Während AMD weiterhin die Grenzen der Rechenleistung und Effizienz verschiebt, steht die Zen 5-Architektur bereit, den Rechenzentrums- und Servermarkt zu revolutionieren.

Die AMD Zen 5-Architektur verwendet ein innovatives modulares Design, das es AMD ermöglicht, maßgeschneiderte Produkte für Desktop-, Server-, Client- und eingebettete Anwendungen zu entwickeln. Die Integration von 4-nm- und 3-nm-Prozesstechnologien stellt sicher, dass Zen5-basierte Produkte für verschiedene Anwendungsfälle optimierte Leistung und Energieeffizienz bieten können.

AMD Zen 5

In AMDs Präsentation auf dem Tech Day 2024 stellte Mark Papermaster bedeutende Fortschritte in der Zen 5-Architektur vor und hob dabei insbesondere die EPYC-CPUs der 5. Generation hervor. Die EPYC-Reihe, die in der zweiten Hälfte des Jahres 2024 auf den Markt kommen soll, verspricht beispiellose Leistung und Effizienz und treibt die Dichte- und Leistungsmetriken auf den Server- und Rechenzentrumsmärkten auf die Spitze.

Die EPYC-CPUs der 5. Generation haben eine deutlich erhöhte Kernanzahl und Threading-Fähigkeit. Zu diesen Verbesserungen gehören auch Verbesserungen der Energieeffizienz, die durch eine fortgesetzte Partnerschaft mit TSMC und einen optimierten Metallstapel ermöglicht wurden. Letzterer hat die thermische und elektrische Leistung deutlich verbessert. Die Architektur nutzt eine erweiterte KI-Beschleunigung durch die Einführung einer neuen Math Acceleration Unit, die eine Verbesserung der Single-Core-AES-XTS-Leistung um bis zu 35 % und bei Single-Core-Maschinenlernaufgaben um bis zu 32 % im Vergleich zu Zen 4 verspricht.

Die architektonischen Verbesserungen in Zen 5 sind umfassend. Die Abruf- und Dekodierungsphasen für Befehle wurden mit erweiterter Verzweigungsvorhersage und dualen Dekodierungspipelines verbessert, um die Latenz zu verringern und die Genauigkeit zu verbessern. Die Integer-Ausführungseinheiten erfahren ein wesentliches Upgrade mit 8-breiten Dispatch-/Retire-Funktionen und einem einheitlicheren ALU-Scheduler, alles innerhalb eines größeren Ausführungsfensters. Zu den Lade-/Speicherverbesserungen gehört ein 48 KB großer 12-Wege-L1-Datencache mit der doppelten maximalen Bandbreite sowohl für den L1-Cache als auch für die Gleitkommaeinheit, die für datenintensive Operationen entscheidend ist.

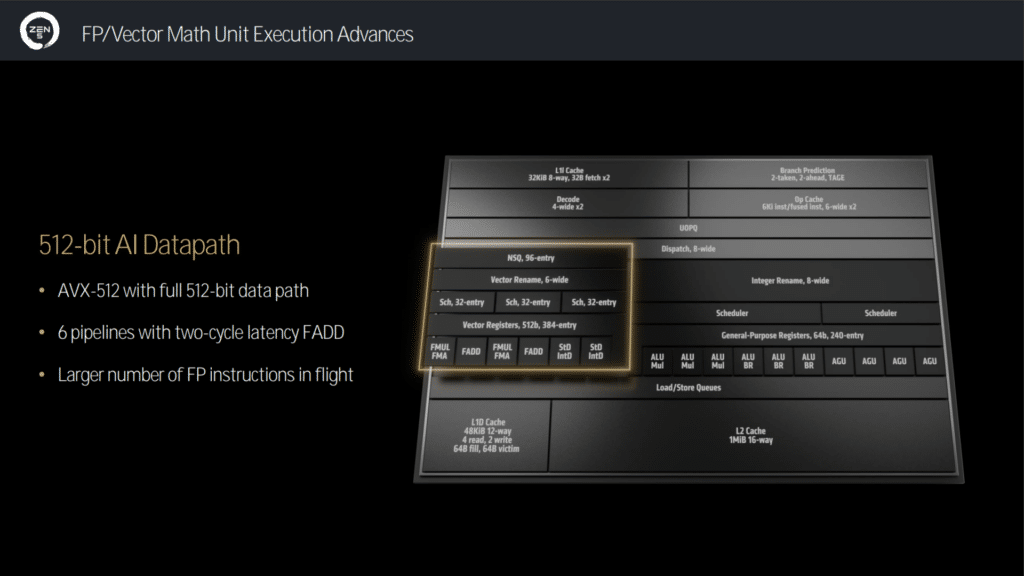

Die Zen 5-Architektur beinhaltet auch erhebliche Verbesserungen der Datenbandbreite. Die Lade-/Speicherverbesserungen mit einem 48 KB 12-Wege-L1-Datencache bieten die doppelte maximale Bandbreite für den L1-Cache und die Gleitkommaeinheit, die für datenintensive Vorgänge unerlässlich ist. Die Fähigkeit der Architektur, mit AVX-512 und einem vollständigen 512-Bit-Datenpfad eine größere Anzahl von Gleitkommaanweisungen im laufenden Betrieb zu verarbeiten, sorgt für erhebliche Leistungssteigerungen bei KI- und Vektor-Workloads.

Auch die Ausführung von Gleitkomma- und Vektormathematikeinheiten wurde erheblich verbessert. Der AVX-512 mit einem vollständigen 512-Bit-Datenpfad und sechs Pipelines (die eine Latenz von zwei Zyklen für Gleitkomma-Addieroperationen bieten) verbessert die Fähigkeit zur Verwaltung gleichzeitiger Gleitkommaanweisungen erheblich. Dies kommt insbesondere Vektor- und KI-Workloads zugute und ermöglicht erhebliche Leistungsverbesserungen bei maschinellem Lernen und datenintensiven Aufgaben. Dies steht im Gegensatz zu Zen 4, wo AMD den 256-Bit-Pfad „doppelt gepumpt“ hat, um eine 512-Bit-Leistung zu erreichen.

Zen 5 bringt eine durchschnittliche IPC-Steigerung von 16 % für Desktop- und Mobilprozessoren im Vergleich zu seinem Vorgänger Zen 4. Dies wird durch architektonische Verbesserungen erreicht, darunter breitere Dispatch- und Ausführungseinheiten, erhöhte Datenbandbreite und verbesserte Prefetching-Algorithmen. Die IPC-Gewinne führen zu realen Leistungsverbesserungen in verschiedenen Anwendungen, von Spielen bis hin zur Inhaltserstellung und maschinellem Lernen.

Auf der GPU-Seite optimiert AMD seine RDNA 3-Architektur weiterhin für Energieeffizienz. AMD verspricht bis zu 32 % mehr Leistung pro Watt als frühere Ryzen-CPUs. Dies wird durch besseres Speichermanagement, doppelt so hohe Rate gängiger Texturoperationen in Spielen und verbesserte Energieverwaltungsfunktionen erreicht.

AMDs Zen 5-Architektur ist eine beeindruckende Weiterentwicklung der Zen-Architektur, insbesondere für die EPYC-Reihe, die verspricht, die Leistungsstandards auf ganzer Linie zu steigern, vom Desktop- und Mobil- bis hin zum Server- und Rechenzentrumsmarkt. Mit erheblichen Verbesserungen bei Kernanzahl, Threading, Energieeffizienz und KI-Beschleunigung in einigen Chips sind die EPYC-CPUs der 5. Generation in der Lage, den wachsenden Anforderungen moderner datenzentrierter Workloads gerecht zu werden.

XDNA

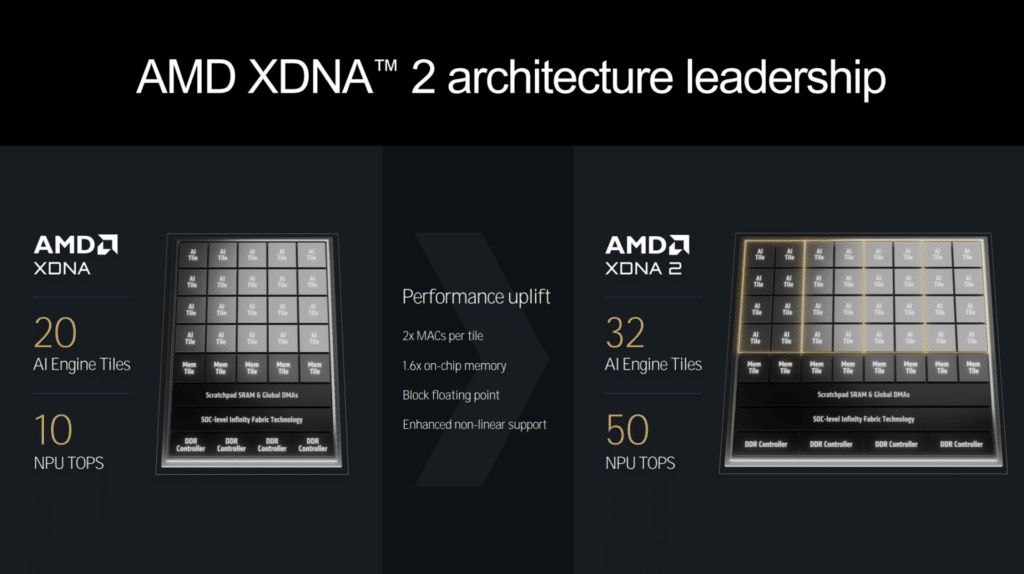

Vamsi Boppana, Senior Vice President der Artificial Intelligence Group, skizzierte das transformative Potenzial der neuen KI-zentrierten Architektur von AMD. Das exponentielle Wachstum und die Spezialisierung von KI-Workloads erfordern innovative Computerarchitekturen, und AMDs Antwort darauf ist die Einführung der XDNA 2-Architektur.

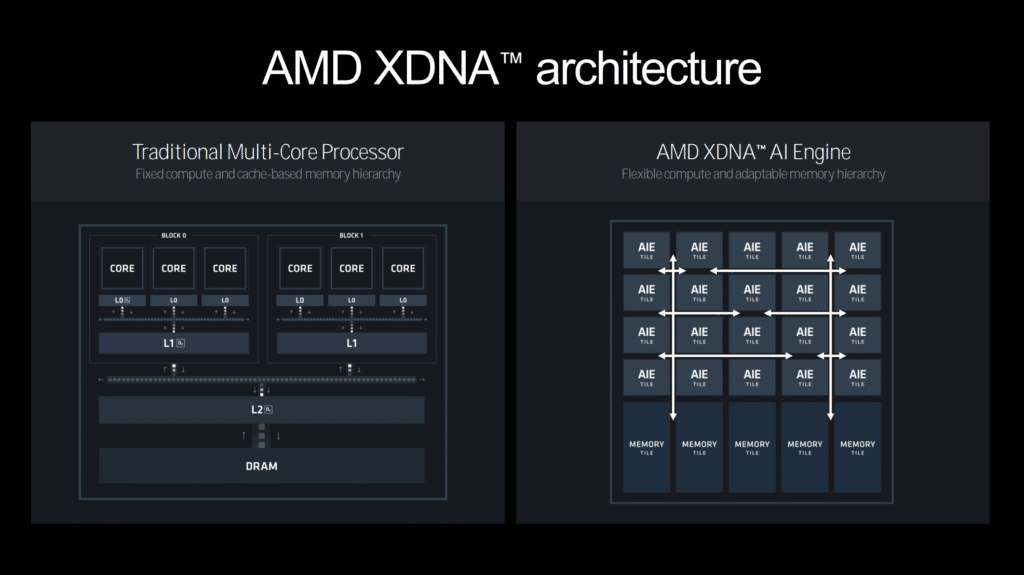

Das Herzstück dieser Innovation ist die AMD XDNA-Architektur, die für ihre langjährige Erfahrung in verschiedenen KI- und DSP-Anwendungen bekannt ist, die Kommunikation, 5G-Bereitstellung, Signalverarbeitung von Verteidigungsradaren, Echtzeit-KI-Verarbeitung für 3D-Ansichten und Bildverarbeitung im Gesundheitswesen umfassen. Die Architektur bewegt sich von traditionellen festen Rechen- und Cache-basierten Speicherhierarchien zu einem flexibleren, anpassbareren Modell. Diese räumliche Rekonfigurationsfähigkeit und die gekachelte Datenflussarchitektur ermöglichen effizientes Multitasking und garantierte Echtzeitleistung.

In der Präsentation wurde der x86-Prozessor von AMD mit integrierter NPU vorgestellt, der für hohe Effizienz und Leistung bei KI-Workloads entwickelt wurde. Die AMD Ryzen KI-Prozessoren der 3. Generation zeichnen sich durch deutliche Verbesserungen bei den NPU-Fähigkeiten aus, erreichen bis zu 50 TOPS (Billionen Operationen pro Sekunde) und verfügen über bis zu 12 CPU-Kerne und 16 GPU-Recheneinheiten. Diese Prozessoren werden über 100 KI-gesteuerte Erlebnisse auf Plattformen wie Adobe, Black Magic und Topaz Labs ermöglichen und sind damit von zentraler Bedeutung für KI-PC-Erlebnisse der nächsten Generation.

Die KI-Engine innerhalb der XDNA 2-Architektur bietet erweiterte Unterstützung für verschiedene Datentypen wie INT8 und Block FP16, was eine hohe Leistung und Genauigkeit in einer Reihe von KI-Anwendungen gewährleistet. Die adaptive KI-Architektur ermöglicht eine skalierbare Integration in das gesamte Produktportfolio von AMD und bietet effizientes Multitasking und garantierte Echtzeitleistung durch räumliche Rekonfigurationsfähigkeit und eine gekachelte Datenflussarchitektur.

Insbesondere Block FP16 ermöglicht einen Drop-In-Ersatz für FP32-Modelle mit wenig bis keinem Genauigkeitsverlust und ist daher für Aufgaben wie Bilderzeugung, Sprachmodelle und Echtzeit-Audio- und Videoverarbeitung äußerst effizient.

Ein herausragendes Merkmal ist die Möglichkeit, das XDNA-Fabric zur Laufzeit zu konfigurieren. Dies ermöglicht Flexibilität bei Datenpfaden und Segmentierung der NPU, um mehrere Modelle unterschiedlicher Größe gleichzeitig auszuführen. Es bietet auch die Flexibilität, KI-gestützte Erlebnisse wie Copilot+ für verbesserte Produktivität und immersive Zusammenarbeit bereitzustellen. Die Integration des einheitlichen KI-Software-Stacks über die CPU-, GPU- und NPU-Komponenten von AMD ermöglicht eine breite Modellunterstützung und optimierte Leistung, sodass Entwickler Tausende von KI-Modellen schnell und effektiv bereitstellen können.

Die AMD XDNA 2-Architektur stellt einen bedeutenden Sprung in der KI-Technologie dar. Mit bis zu acht gleichzeitigen räumlichen Streams verdoppelt sie die Energieeffizienz früherer Generationen. Dies macht die Lösung von AMD leistungsstark und hocheffizient und ebnet den Weg für eine neue Ära von KI-Anwendungen in PCs und darüber hinaus.

Die AMD Ryzen AI-Prozessoren der 3. Generation bieten außerdem verbesserte Sicherheit durch die Einführung neuer Trusted IO-Funktionen. Diese Sicherheitsverbesserung ist entscheidend für den Schutz vertraulicher Daten und die Gewährleistung einer zuverlässigen Leistung in KI-gesteuerten Anwendungen und unterstreicht AMDs Engagement für sichere und effiziente KI-Lösungen.

AMD Zen 5 und XDNA 2 Spezifikationen

| Zen 5 Architektur | |

| Merkmal | Details |

| Prozesstechnologie | 4 nm und 3 nm |

| Kernzählung | Bis zu 192 Kerne |

| Thread Count | Bis zu 384 Fäden |

| Cache | 48 KB 12-Wege-L1-Datencache |

| Bandbreite | Verdoppeln Sie die maximale Bandbreite für L1-Cache und Gleitkommaeinheit |

| Integer-Ausführung | 8-breites Dispatch/Retire, 6 ALU, 3 Multiplikationen |

| Gleitkommaausführung | AVX-512 mit vollem 512-Bit-Datenpfad, 6 Pipelines |

| KI-Beschleunigung | Neue Einheit zur Beschleunigung der Mathematik |

| IPC-Aufwertung | 16 % durchschnittlicher IPC-Anstieg gegenüber Zen 4 |

| Leistungsgewinne | 35 % Verbesserung bei Single-Core-AES-XTS, 32 % Steigerung bei Machine-Learning-Aufgaben |

| Energie-Effizienz | Optimiert für Leistung/Watt mit verbessertem Metallstapel |

| Produktanwendungen | Desktop, Mobil, Server und Rechenzentrum |

| XDNA 2-Architektur | |

| KI-Engine-Kacheln | max. 32 |

| KI-Leistung | Bis zu 50 TOPS |

| Kernzählung | Bis zu 12 CPU-Kerne |

| GPU Compute Units | max. 16 |

| Unterstützte Datentypen | INT8, Block FP16 |

| Wirkungsgrad | Doppelte Energieeffizienz im Vergleich zur vorherigen Generation |

| Gleichzeitige Streams | max. 8 |

| Sicherheit | Neue Trusted IO-Funktionen |

| Software-Stack | Einheitlicher KI-Software-Stack für CPU, GPU und NPU |

| Echtzeitleistung | Garantierte Echtzeitleistung mit räumlicher Architektur |

| Anwendungen | Gaming, Unterhaltung, persönliche KI-Assistenz, Content-Erstellung, Unternehmensproduktivität |

Zen 5 Desktop-Übertaktung mit Curve Shaper

AMDs Curve Optimizer, ein Markenzeichen der Ryzen 7000-Serie, ermöglicht es Benutzern, PMFW/PBO-fähige dynamische Spannungsskalierung oder Unterspannung zu aktivieren. Dieses leistungsstarke Tool verschiebt die Spannungskurve dynamisch durch anpassbare „Curve Optimizer“-Schritte und sorgt so für variable Spannung über das gesamte Frequenzspektrum, wobei bei höheren Frequenzen mehr Spannung zugewiesen wird. Benutzer können diese Optimierung pro Kern, pro CCD oder pro CPU anwenden und so die Leistung und Effizienz ihrer CPU präzise steuern.

Aufbauend auf den Grundlagen von Curve Optimizer führt AMD Curve Shaper ein, eine ausgeklügelte Erweiterung, mit der Benutzer die zugrunde liegenden Spannungskurven neu formen können, um das Unterspannungspotenzial zu maximieren. Curve Shaper verwendet dieselben Schritte wie sein Vorgänger. Dennoch bietet es Benutzern die Flexibilität, selektiv Schritte aus 15 unterschiedlichen Frequenz-Temperatur-Bändern (drei Temperaturbänder und fünf Frequenzbänder) hinzuzufügen oder zu entfernen. Diese Feinabstimmungsfunktion ermöglicht es Benutzern, die Spannung in stabilen Bändern weiter zu reduzieren und gleichzeitig in Bereichen, in denen Instabilitäten beobachtet werden, Spannung hinzuzufügen. Die neu geformte Kurve wird gleichmäßig auf alle Kerne angewendet und kann mit Curve Optimizer weiter angepasst werden.

Abschließende Gedanken

Der AMD Tech Day 2024 war ein großartiges Event, bei dem wir die sehr geschätzte Gelegenheit hatten, tief in die Geschichte der Ingenieure hinter den Produkten einzutauchen. AMDs neueste Fortschritte mit der XDNA 2-Architektur und Zen 5-CPUs unterstreichen sein Engagement, die KI- und High-Performance-Computing-Revolution anzuführen. Mit bahnbrechenden Verbesserungen bei Kernanzahl, Threading, Energieeffizienz und KI-Beschleunigung ist AMD bereit, Industriestandards neu zu definieren und den wachsenden Anforderungen moderner datenzentrierter Workloads gerecht zu werden und umfassende Leistung für Desktop-, Mobil-, Server- und Rechenzentrumsanwendungen sicherzustellen.

Beteiligen Sie sich an StorageReview

Newsletter | YouTube | Podcast iTunes/Spotify | Instagram | Twitter | TikTok | RSS Feed